数字集成电路主要由逻辑门电路、触发器、寄存器等构成,下面介绍这些电路的识图方法。

1. 逻辑门电路

逻辑门电路除了可以实现各种逻辑处理,还可以用于多谐振荡器和模拟放大电路,常用的逻辑门电路主要有与门、或门非门、与非门、或非门、异或门、异或非门等。

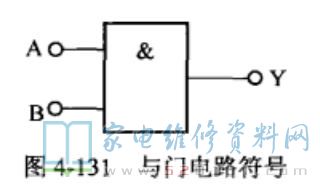

(1)与门

与门电路的电路符号如图4-131所示。它的逻辑关系是Y=AB,也就是A、B两个输入信号都为高电平时,输出端输出的信号Y才能为高电平,否则Y就为低电平。

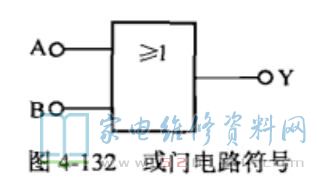

(2)或门

或门电路的电路符号如图4-132所示。它的逻辑关系是Y=A+B,也就是A、B两个输入信号的其一为高电平时,输出端输出的信号Y就为高电平:若想Y为低电平,则需要A、B两个信号都为低电平。

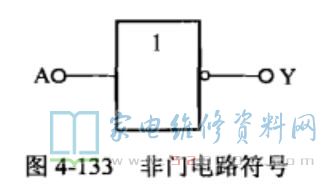

(3)非门

非门电路的电路符号如图4-133所示。它的逻辑关系是Y= ,也就是输出端信号Y和输入信号A相反,因此非门也叫反相器或倒相器。

,也就是输出端信号Y和输入信号A相反,因此非门也叫反相器或倒相器。

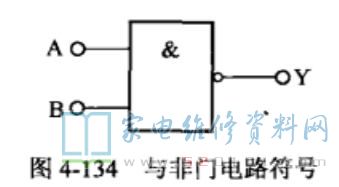

(4)与非门

与非门电路的电路符号如图4-134所示。它的逻辑关系是Y= ,该逻辑关系和与门电路的逻辑关系正好相反:只有A、B两个输入信号都为高电平时,输出信号Y才能为低电平,否则Y为高电平。

,该逻辑关系和与门电路的逻辑关系正好相反:只有A、B两个输入信号都为高电平时,输出信号Y才能为低电平,否则Y为高电平。

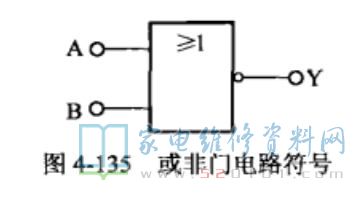

(5) 或非门

或非门电路的电路符号如图4-135所示。它的逻辑关系是Y= ,该电路的逻辑关系与或门的逻辑关系正好相反:只有A、B两个信号都为低电平时,输出端信号Y才能为高电平;而A、B两个输入信号的其一为高电平时,Y就为低电平。

,该电路的逻辑关系与或门的逻辑关系正好相反:只有A、B两个信号都为低电平时,输出端信号Y才能为高电平;而A、B两个输入信号的其一为高电平时,Y就为低电平。

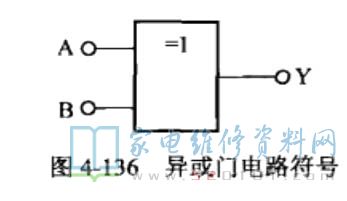

(6)异或门

异或门电路的电路符号如图4-136所示。它的逻辑关系是Y=  ,也就是A、B两个输入信号不同时,输出信号Y就为高电平:若A、B两个信号相同时,Y则为低电平。

,也就是A、B两个输入信号不同时,输出信号Y就为高电平:若A、B两个信号相同时,Y则为低电平。

2. 触发器

触发器是实现时序处理的主要电路之一,常见的触发器主要有RS触发器、JK触发器、D触发器、单稳态触发器、施密特触发器等。

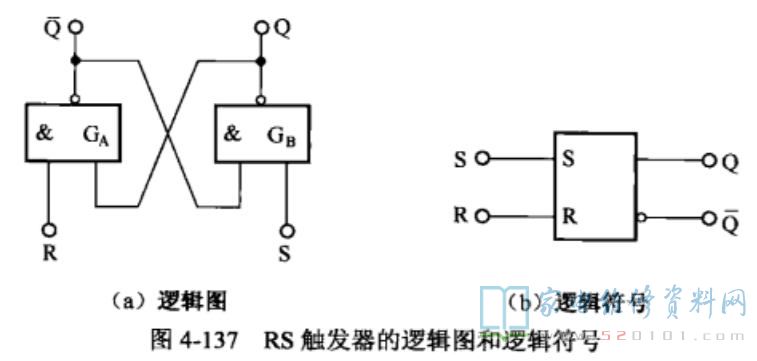

(1) RS触发器

RS触发器是最基本的触发器,它的逻辑图和逻辑符号如图4-137所示。

通过图4-137可以看出,RS 触发器由两个与非门构成,所以可按照与非门的逻辑关系进行分析。

在S=0、R= 0状态,由于S、R端均输入低电平信号,两个与非门的输出端Q、 的电位都会变为高电平,当低电平过后使R、S端同时输入高电平信号时,会导致输出端Q、

的电位都会变为高电平,当低电平过后使R、S端同时输入高电平信号时,会导致输出端Q、 输出的电位紊乱,所以这种状态是不允许出现的。

输出的电位紊乱,所以这种状态是不允许出现的。

在S=0、R= 1状态,由于S端输入低电平信号,Q端电位变为高电平,而R端输入的信号也为高电平,所以 端的电位变为低电平。

端的电位变为低电平。

在S= 1、R= 0状态,由于R端输入低电平信号,Q端电位变为高电平,而S端输入的信号也为高电平,所以Q端的电位变为低电平。

在S=1、R=1.状态,Q、Q端的电位会保持原有的状态而不发生变化,所以这种状态也叫记忆状态。

提示:分析触发器的逻辑关系时,通常将Q=1、 =0的状态称为“1” 态,将Q=0、

=0的状态称为“1” 态,将Q=0、 =1的状态称为“O”态。因此,S端被称为置“1”端,R端被称为置“0”端,也就是S=0时Q=1,R=0时Q=0。

=1的状态称为“O”态。因此,S端被称为置“1”端,R端被称为置“0”端,也就是S=0时Q=1,R=0时Q=0。

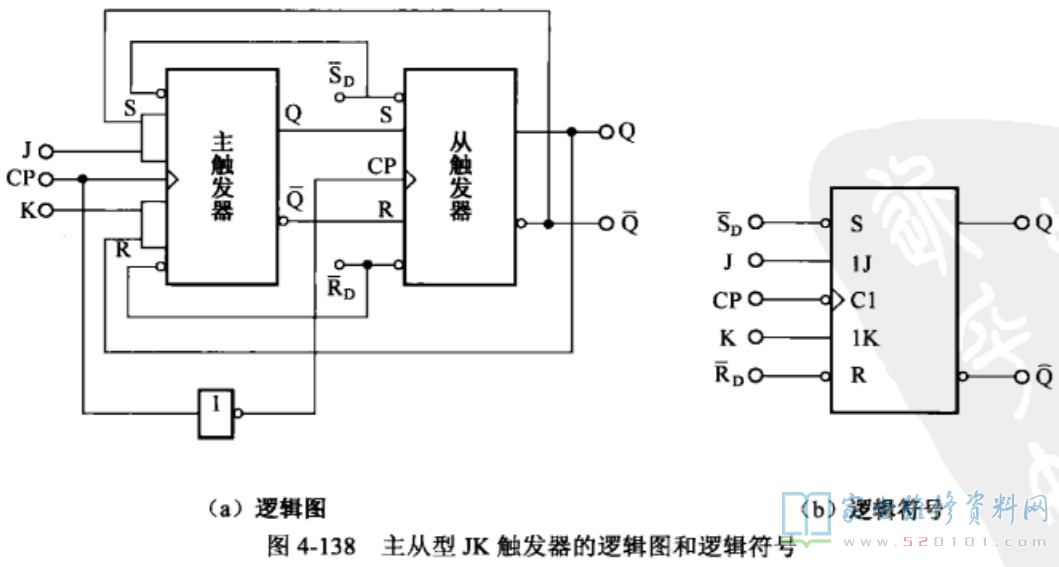

(2) JK触发器

JK触发器是一种功能完善、应用广泛的双稳态触发器。

图4-138 (a)所示的是一种典型结构的JK触发器。它由两个可控的RS触发器串联构成,分别称为主触发器和从触发器,所以此类JK触发器也叫主从型JK触发器。J、 K是信号输入端; CP是时钟信号输入端,由它控制主触发器和从触发器的翻转。

当CP=0时,主触发器状态不变,从触发器输出状态与主触发器的输出状态相同。当CP=1时,输入信号J K的电位高低影响主触发器的状态,而从触发器状态不变。

当CP从1变为0时,主触发器输出的状态传送到从触发器,即主、从触发器是在CP下降沿到来时才能控制触发器翻转的。主从型JK触发器的逻辑分析如下。

①J=1 K=l时,设触发器的初始状态在时钟脉冲到来前(即CP=0)为0。这时主触发器的R=K=0、S=J=1,时钟脉冲到来后(即CP=1)主触发器翻转成为1态。当CP从: 1跳变为0时,主触发器状态不变,从触发器的R=0、S=1,所以它会翻转成1态。反之,若设触发器的初始状态为1,则主、从触发器就会翻转成0态。因此,主从型触发器在J= 1、K=1的情况下,来一个时钟脉冲就会翻转一 次,也就是在此状态下该触发器具有计数功能。

②J=0、K= 0时,设触发器的初始状态为0,当CP=1时,由于主触发器的R=0、S= 0,它的状态保持不变。当CP跳变为0时,由于从触发器的R=1、S=0,它的输出为0态,即触发器始终保持0态不变;如果初始状态为1,则触发器会始终保持1态不变。

③J=1、K=0时,设触发器的初始状态为0。当CP=1时,由于主触发器的R=0、S=1,它翻转成1态。当CP跳变为0时,由于从触发器的R=0、S= 1,所以也翻转成1态。如果触发器的初始状态为1,当CP=1时,由于主触发器的R=0、S=0,它保持原态不变;在CP从1跳变为0时,由于从触发器的R=0、S= 1,也会保持1态不变。

④J=0、K=1时,设触发器的初始状态为1态。当CP=1时,由于主触发器的R= 1、S=0,它翻转成0态。当CP下跳时,从触发器也翻转成0态。如果触发器的初始状态为0态,当CP=1时,由于主触发器的R=0、S=0,它保持原态不变;在CP从1跳变为0时,由于从触发器的R=1、S=0,也保持0态。

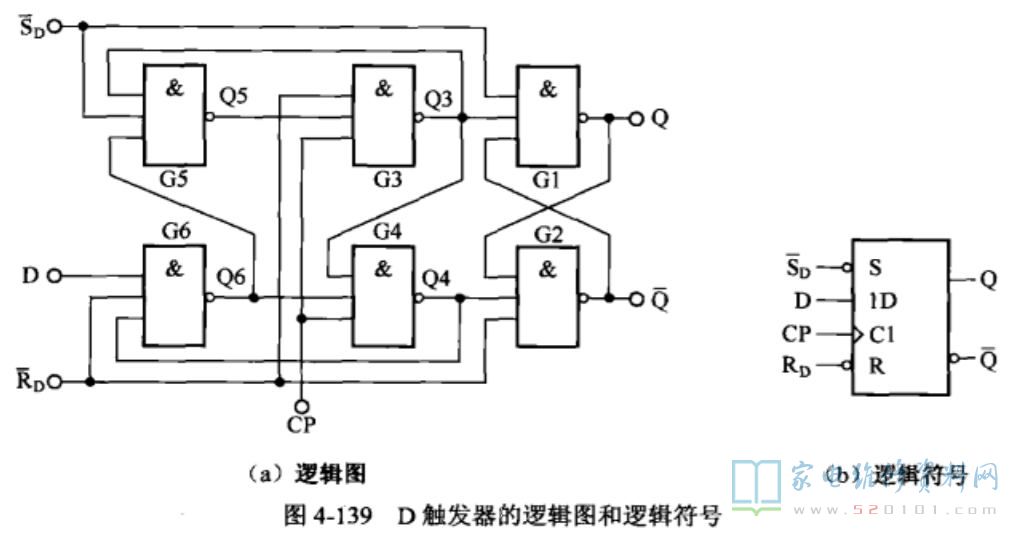

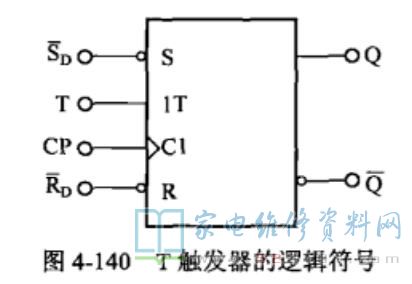

(4) T触发器

T触发器是在D触发器基础上开发的。T触发器的逻辑符号如图4-140所示。该触发器的逻辑关系是:当T=1时,该触发器处于计数状态,每来一个时钟脉冲CP,触发器翻转一次;当T=0时,该触发器处于记忆状态,时钟脉冲即使到来也不会影响触发器的状态。

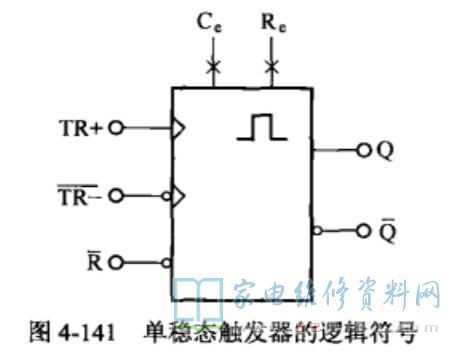

(5)单稳态触发器

单稳态触发器的逻辑符号如图4-141所示。图中的TR+是上升沿触发脉冲输入端, 是下降沿触发脉冲输入端,Q为输出端,

是下降沿触发脉冲输入端,Q为输出端, 为反相输出端。单稳态触发器的特点是,当它被触发后就会输出一个频率固定的矩形脉冲,然后自动返回。频率由Ce、Re。端外接的阻容元件参数来决定,即f= 1/0.69ReCe。

为反相输出端。单稳态触发器的特点是,当它被触发后就会输出一个频率固定的矩形脉冲,然后自动返回。频率由Ce、Re。端外接的阻容元件参数来决定,即f= 1/0.69ReCe。

(6)施密特触发器

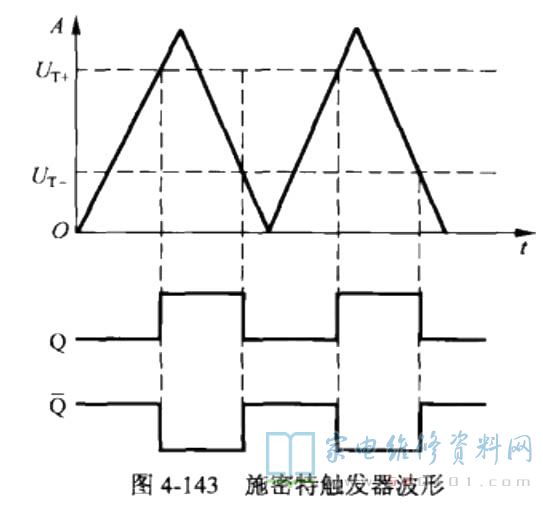

施密特触发器有同相输出和反相输出两种类型,它们的逻辑符号如图4-142所示。施密特触发器的特点是具有滞后电压特性,即当输入电压升高到正向阈值电压Ut+时触发器翻转,当输入电压下降到负向阙值电压Ut-时触发器再次翻转,波形如图4-143所示。

3. 寄存器

在数字电路中,用来存放二进制数据或代码的电路称为寄存器。寄存器是由具有存储功能的触发器组合起来构成的。一个触发器可以存储一位二进制代码。存放N位二进制代码的寄存器,需用n个触发器来构成。寄存器主要有基本寄存器和移位寄存器两种。基本寄存器主要设置在单片机内部,所以不作介绍,而移位寄存器被许多电子产品用于操作显示电路,下面简单介绍移位寄存器。

移位寄存器中的数据可以在移位脉冲作用下-次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。

目前常用的集成移位寄存器种类很多,如74164、74165、74166 均为八位单向移位寄存器,74195为四位单向移位寄存器,74194 为四位双向移位寄存器,74198 为八位双向移位寄存器。

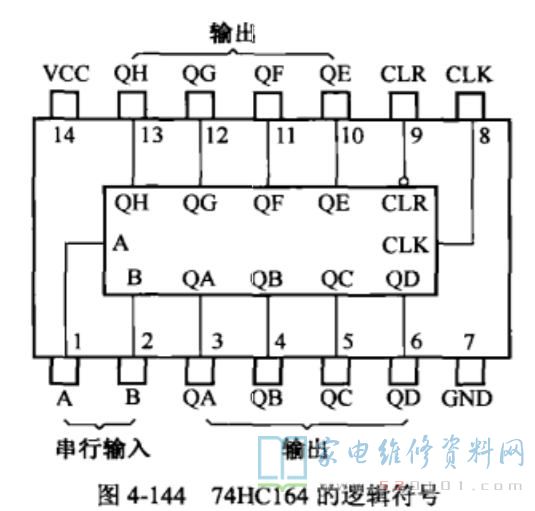

图4-144所示是74HC164的逻辑符号。图中A、B为串行码信号输入端,CLR为清零信号输入端,CLK为时钟信号输入端。当时钟信号处于上升沿期间,A、B相与后的状态依次由QA移向QH。

网友评论